一、EPM240T100C5N介绍

厂商型号:EPM240T100C5N

品牌名称:ADI(亚德诺)

元件类别:CPLD复杂可编程逻辑器件

封装规格:TQFP100_14X14X05P

型号介绍: 瞬变非易失性cpld

二、EPM240T100C5N概述

MAX®II系列瞬变非易失性cpld基于0.18 μ m, 6层金属闪光过程,密度从240到2210逻辑元件(LEs)(128到2210等效宏单元)和8 Kbits的非易失性存储。与其他CPLD架构相比,MAX II器件提供了高I/O计数、快速性能和可靠的匹配。MAX II设备具有MultiVolt核心、用户闪存(UFM)块和增强的系统内可编程性(ISP),旨在降低成本和功耗,同时为总线桥接、I/O扩展、上电复位(POR)和排序控制以及设备配置控制等应用提供可编程解决方案。

特点:

低成本、低功耗CPLD

■即时性、非易失性架构

■待机电流低至29 μ A

■提供快速传播延迟和时钟到输出时间

■提供4个全局时钟,每个逻辑阵列块(LAB)提供2个时钟

非易失性存储的UFM块高达8 Kbits

■多伏特磁芯可向设备提供3.3 V/2.5 V的外部供电电压

或1.8 V

■多伏特I/O接口,支持3.3 v、2.5 v、1.8 v、1.5 v逻辑电平

■总线友好的架构,包括可编程的转换速率,驱动强度,套管,和可编程的上拉电阻

■Schmitt触发允许噪声容忍输入(每针可编程)

■I/ o完全符合外围组件互连专用(Peripheral Component Interconnect Special)

兴趣小组(PCI SIG) PCI本地总线规范,3.3-V版本2.2

66兆赫频率

■支持hot-socketing

■内置联合测试动作组(JTAG)边界扫描测试(BST)电路

符合IEEE Std. 1149.1-1990标准

■ISP电路符合IEEE标准1532

三、EPM240T100C5N中文参数/资料

分别: CPLD(复杂可编程逻辑器件)

系列:MAX® II

包装:托盘

可编程类型:系统内可编程

延迟时间 tpd(1) 最大值:4.7 ns

供电电压 - 内部:2.5V,3.3V

逻辑元件/块数:240

宏单元数:192

I/O 数:80

工作温度:0°C ~ 85°C(TJ)

安装类型:表面贴装型

封装/外壳:100-TQFP

四、EPM240T100C5N原理图、料号解释图

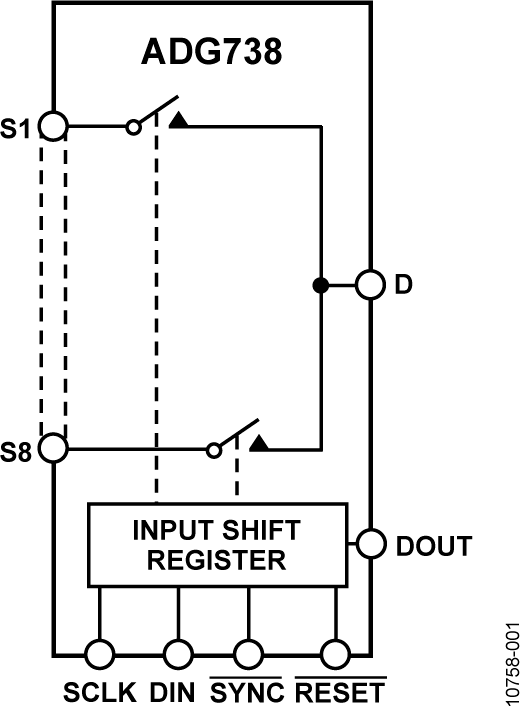

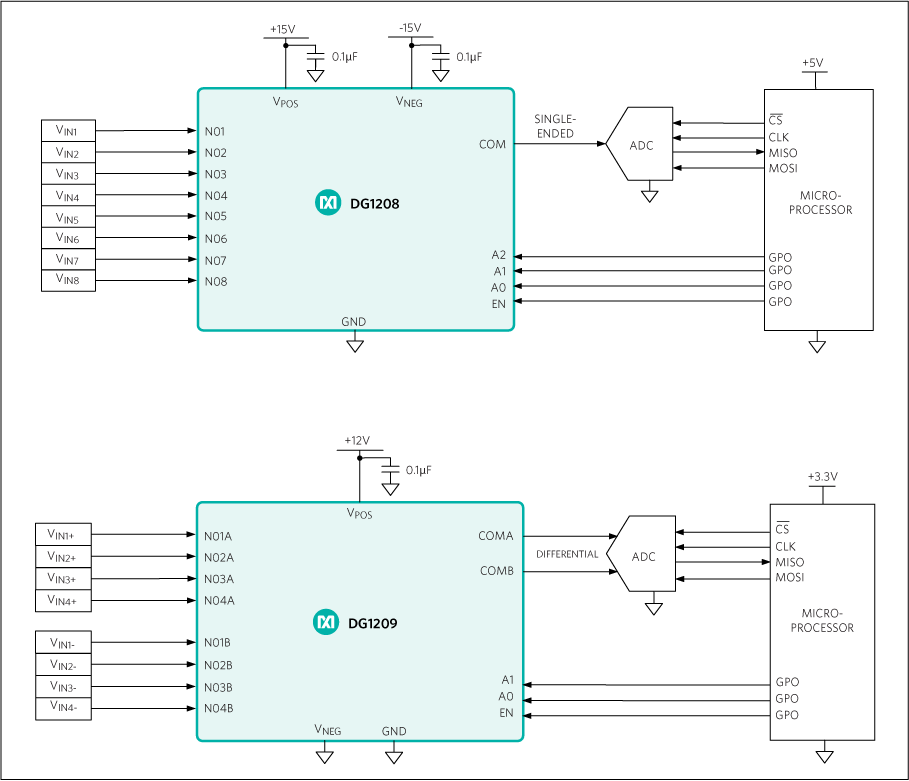

EPM240T100C5N电路图(原理图)

料号解释图

购物车中还没有商品,赶紧选购吧!

购物车中还没有商品,赶紧选购吧!